### **BARLEC** RICHFIELD

Barlec-Richfield Limited Foundry Lane Horsham West Sussex RH13 5PX Telephone 0403 51881 Telex 877222 Facsimile 0403 41746

1987 CCD Solid State Imaging Technology

Schlumberger

## 1987 CCD Databook

CCD Solid State Imaging Technology

**FAIRCHILD WESTON**

**CCD IMAGING DIVISION**

CCD Imaging and Signal Processing Catalog and Applications Handbook

Fairchild Weston Systems, Inc. CCD Imaging Division. 810 W. Maude Ave., Sunnyvale, California 94086 (408) 720-7600, TWX 910-373-2110

Printed in U.S.A.

1987. Fairchild Weston reserves the right to make changes in the circultry or specifications at any time without notice.

Manufactured under one of the following U.S. Patents: 2981877, 3015048, 3084167, 3108359, 3117260; other patents pending.

Fairchild Weston cannot assume responsibility for use of any circultry described other than circultry embodied in a Fairchild Weston product. No other circuit patent ilcenses are implied.

#### FAIRCHILD WESTON

CCD IMAGING DIVISION

#### **Table of Contents**

| Intro          | 5           |                           |

|----------------|-------------|---------------------------|

| Line           | 8           | <b>)</b>                  |

| Line           | 9           | )                         |

| (              | 11          | <b>)</b>                  |

|                |             |                           |

|                | 39          | ı                         |

| -              | 47          | i                         |

|                | 59          |                           |

| - 1            | 69          |                           |

|                |             |                           |

| 2              | •••••••• 91 |                           |

| 100            |             |                           |

|                |             | 229                       |

|                | 111         |                           |

| Are            |             | 232                       |

|                |             | 235                       |

| CC             |             | 238                       |

|                |             | 241                       |

| - 4            |             | 243                       |

|                |             |                           |

|                |             |                           |

| Line           |             |                           |

| 1              |             |                           |

| 5              |             |                           |

|                |             |                           |

| Are            |             | 248                       |

| Car            |             | 240                       |

| (              |             | 249                       |

| (              |             | 245                       |

| 4              |             | 250                       |

| 4              |             | 250 251                   |

| 4              |             | 231                       |

| Sig            |             | Quality Assurance Program |

| CCD321A/B      |             | 202                       |

| CCD321VM       |             |                           |

| CONTRACT A IAI |             |                           |

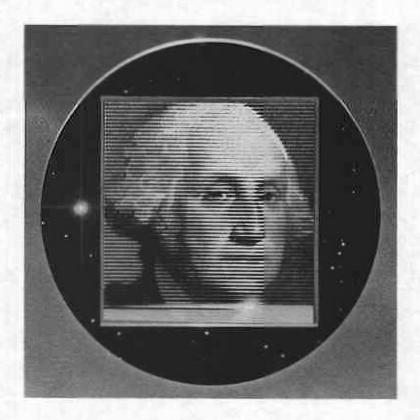

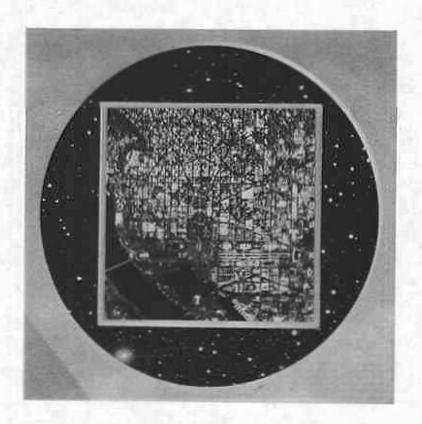

L'Enfant's street plan for Washington, D.C. (above) approximating Paris, is obvious in this view made by the French SPOT Image Corporation's remote sensing satellite system ... a system which relies on CCD technology. Fairchild Weston's CCD Imaging Division was a supplier to SPOT.

Created for commercial and environmental applications, SPOT is able to "see" 1400 square miles in one 10-second pass, or more than 25 conventional high-altitude serial photographs.

Aerial photography, itself, was made possible by the inventions of Sherman Mills Fairchild—shutter and timing mechanisms, camera systems and closedcabin aircraft (right).

Fairchild founded several companies which evolved leadership roles in aircraft development, defense electronics & systems, optics, semiconductor manufacturing, as well as CCD Imaging Technology.

## The Fairchild Evolution of CCD Imaging

#### Fairchild Camera & Instrument Corporation

During World War II, the New York photography operation designed and manufactured 90 percent of the aerial cameras used by all Allied forces, and the firm adopted the name Fairchild Camera and Instrument Corporation.

After the war, products related to the original camera manufacturing operations made Fairchild a major US government supplier of aerial cameras, surface surveillance systems and other defense related products.

#### **Fairchild Semiconductor**

In the late 1950's, the company sponsored a small group of young scientists in California developing new processes for the manufacture of transistors,

Their goal was to develop, mass produce and market semiconductor components that could meet the most stringent customer requirements, and in 1959 the Planar process was introduced.

The Fairchild CCD Imaging Division, which successfully developed and delivered the first commercial charged-coupled device in 1973, actually traces its roots back through two branches of the corporate tree to the noted American inventor, scientist and industrialist, Sherman Mills Fairchild in the early 1920's.

Fairchild's first invention was an efficient between-thelens camera shutter and associated timing mechanism which enabled accurate aerial photography for the first time.

Fairchild's additional inventions in aircraft technology (including the first enclosed cabin airplane, the first with folding wings, the first with hydraulically-operated landing gear and brakes) were consolidated into the Fairchild Aviation Corporation.

In 1936, aircraft products were separated from the camera related operations in New York as the Fairchild Engine and Airplane Corporation in Maryland.

By the mid-70's Fairchild had become the third largest US supplier of semiconductors, and the parent, Fairchild Camera & Instrument Corp., was all but eclipsed by the offspring Semiconductor Division and its accelerating technology.

For example, at the Palo Alto Research Lab, a major effort was being made to advance CCD Imaging technology and to speed process development of manufacturing a broad range of solid-state sensing devices.

Meanwhile in Syosset, New York, the company was Introducing a panoramic aerial camera with an exclusive rotating optical prism, making possible the first 180-degree, horizon-to-horizon aerial photograph.

#### Schlumberger Limited

In 1979, Fairchild became a part of Schlumberger Limited, a company which, like Fairchild, had grown successfully through innovations in science and industry.

Shortly after the turn of the century, brothers Conrad and Marcel Schlumberger's experiments with surface electrical instruments led to an "electric log" process for French oil exploration that demonstrated conclusively that geological formations penetrated by the drill could be identified by electrical measurements.

Today, Schlumberger is an international company providing oil and gas drilling and production services; energy measurement and control equipment; Instruments, components and computer-aided design; and manufacturing and control systems.

#### Fairchild Weston Systems, Inc.

Fairchild Weston Systems, descendant of the former Fairchild Camera & Instrument Corporation, continues to carry the mantle of the original camera operation and to expand its technology base as world leader in the design, development and fabrication of high technology electronic, photographic and electro-optical systems for defense-related applications.

#### **CCD Imaging Division**

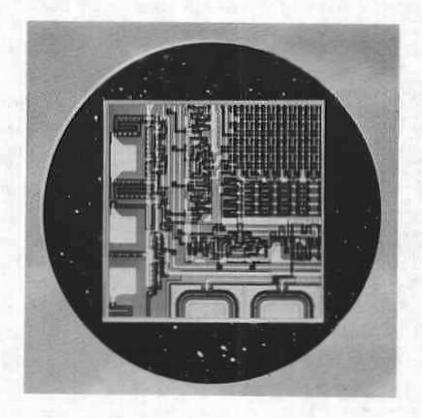

The original buried-channel CCD product technology was transferred from the R&D operation to the CCD imaging volume production environment late in the 1970's with the requisite efforts in development and production engineering in order to produce a full line of linear and area sensors, cameras and camera subsystems as well as ancillary devices in signal processing and interface systems.

In 1985, CCD Imaging was incorporated into the Electro-Optical Systems Group of Fairchild Weston as a natural complement to the continuing program of solid-state TV camera development for NASA and other high-technology users. The first pictures ever taken of a space shuttle in orbit were made by a Fairchild Weston miniature color TV camera mounted on a pallet satellite.

Today, Fairchild Weston's CCD Imaging Division provides sophisticated devices and systems for inspection, measurement, surveillance, telecine, facsimile and optical character recognition in industry, science, medicine, defense and many other fields.

In numerous applications—from food processing to astronomy, from robotics to cartography—the CCD imaging Division continues to spearnead the CCD technological revolution with a wide selection of devices and camera systems.

#### **Custom Engineering Services**

The CCD Division's technical staff of highly experienced engineers is available for special requirements in several areas.

#### **CCD Custom Specifications**

The performance levels of standard products have been chosen to meet most applications. However, some systems may require devices with tighter specifications—lower dark signals, more uniform photoresponse, higher responsivity or some other parameter not included in a standard product.

### Custom & Semicustom Options Infrared Performance

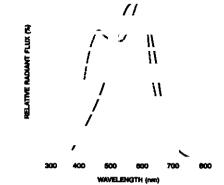

Silicon CCD photosites are optimized for visible light (400-700nm). Although silicon photosites have substantial responsivity in the near-IR (700-400nm), spatial resolution (MTF) degrades severely as wavelength decreases beyond about 700nm. Maximum useable wavelengths are generally in the 800-900nm range. Many light sources (tungsten lamps, sunlight, etc.) have strong IR components. Hence many CCD imaging systems use an optical low-pass filter to eliminate the IR components of the incident illumination.

These limits may be extended up to 30% by various design and manufacturing techniques on a custom application basis.

Fairchild Weston-CCD has also developed prototype sensors using platinum silicide Schottky barrier technology which extend IR performance out to  $5.5\mu m$ .

#### **Ultraviolet Performance**

The newest CCD designs (CCD134, 145, 181, etc.) have at least twice the quantum efficiency in the near-UV (300~400nm) as older designs. Quantum efficiencies of >50% at 400nm are typical.

This improvement can be applied to many current devices and to custom designs on a custom application basis.

Very High Data Rates The standard product assortment of line-scan image sensors include data rate capabilities exceeding 20 MHz sample rate. Since the data rate is limited by the output amplifier, some of our devices—using the charge output directly—have been operated at over 60 MHz.

Even higher effective data rates are possible in custom designs using multiple outputs where each output could run at up to 15-20 MHz and the total data rate is a function of the number of outputs employed.

Long Linear Arrays The longest device currently available in the standard product line is the CCD151 linear sensor—3456 pixels in a row. Longer contiguous lines of pixels can be provided on a custom basis up to the limits of the 4-inch wafer.

Even longer linear configurations can be achieved by staggering devices to produce the desired number of pixels. Various optical techniques, such as beamsplitters, can be employed to create a longer sense line.

The ends of two linear arrays or multiple linear arrays may be joined to achieve a very long sense area, but a few pixels will be lost at the butt joint itself. Fiber bundles can be used in a lens-less system for ultra long, high resolution sense lines with no loss, however.

Fiber Optics Face Plates Most Fairchild Weston CCD linear and area sensors can be fitted with a fiber optics face plate to efficiently couple the optical signal from an image intensifier or other component. (The CCD222 TV image sensor is currently available with such an option.)

Special packaging Some applications require special packages to match unique environments. Fairchild engineers are available to determine the range of possibilities.

Special Screenings Military and space programs often require special screening to meet MIL SPEC 883C or similar applications. Fairchild Weston CCD Imaging Division has considerable experience in screening devices to these specifications.

Other Custom Capabilities Fairchild Weston's CCD staff engineers can provide assistance in other areas as well—AR coated windows, cryogenic temperature operation, special window materials, IR-coated windows, etc. We invite you to consult our experienced sales and application people to discuss a particular requirement.

## Linear Imaging Sensor Selection Guide

#### **LINEAR IMAGE SENSOR SELECTION GUIDE**

|               |                     |                    |                     | Maximum            |                          |                                 | EATURES                    | ]                         | - |

|---------------|---------------------|--------------------|---------------------|--------------------|--------------------------|---------------------------------|----------------------------|---------------------------|---|

| CCD<br>Device | Number of<br>Pixels | Pixel Size<br>(µm) | Pixel Pitch<br>(µm) | Data Rate<br>(Mhz) | Very Low<br>Light Levels | Anti-Blooming<br>& Int. Control | Correlated<br>Double Samp. | Extended Blue<br>Response |   |

|               |                     | 13 × 17            | 13                  |                    |                          |                                 | •                          | 1                         |   |

|               |                     | 13 × 13            |                     | 20.0               |                          |                                 |                            | 1                         |   |

|               |                     | 13 × 13            | 13                  |                    |                          |                                 |                            | 1                         |   |

|               |                     | 13 × 13            | 13                  |                    |                          |                                 |                            | - 1                       |   |

| 4             |                     | 13 × 13            |                     |                    |                          |                                 | /                          | 1                         |   |

|               |                     | 10 × 13            | 10                  | 2.0                |                          |                                 | /                          | 1                         |   |

|               |                     | 13 × 13            | 13                  | 5.0                |                          | <b>*</b>                        | /                          | , 1                       |   |

|               |                     | 13 × 13            | 13                  |                    |                          |                                 | •                          |                           |   |

|               |                     | 10 × 10            | 10                  |                    | ,                        |                                 | ,                          | ,                         |   |

|               |                     |                    |                     |                    |                          |                                 | -                          | 1                         |   |

<sup>+</sup> Limited demand product. CCD123 is recommended for new designs.

#### **Number of Pixels:**

The desired system resolution determines how many pixels are needed on the CCD. Devices are available with up to 3456 pixels (CCD151). Should more pixels be desired, two or more CCDs may be optically butted.

#### Data Rate:

The typical maximum data rate for  $f_{deta}$  is given. Devices with data rates of 10MHz or greater have two outputs —one for even numbered pixels and one for odd. The minimum exposure time for a device with N pixels is about (20 + N)/f\_DATA.

#### Pixel Size and Spacing:

The system optical aperture size and sensitivity desired determine which pixel size is necessary.

#### Sensitivity at Very Low Light Levels:

These devices are ideal for rapidly detecting changes in illumination at the lowest illumination levels. They are optimized for minimal retention of signal charge in photosites.

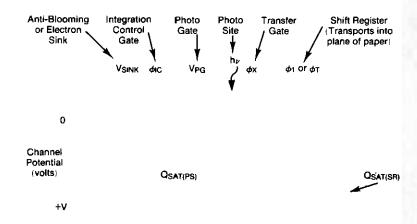

#### Anti-Blooming/Integration Control:

For applications in which the dynamic range of the scene occasionally exceeds the dynamic range of the device, anti-blooming is recommended. This feature prevents extremely bright sections of the image from causing overflow of the CCD shift register. Integration control allows the optical signal integration time to be less than the exposure time. See application notes for details.

#### **Extended Blue Response:**

Devices with extended blue response have 50-100% greater responsivity at 400nm than previous devices. These devices are recommended for applications in which much of the image information is in the blue region.

#### Correlated Double Sampling (CDS) Compatible:

Correlated double sampling is a technique for increasing the signal-to-noise ratio of a CCD-A/D system. Most Fairchild CCDs can use CDS. CDS can only be used with the internal sample and Hold disabled and externally supplied reset clock. See application notes for details.

## Linear CCD Sensors

Fairchild Weston's advanced buried-channel CCD technology allows line scan sensors to offer excellent charge-transfer efficiency at high data rates with low noise, high S/N ratios and relatively small die sizes.

Line scan sensors are useful in document scanning systems for optical character recognition (OCR) and facsimile data acquisition as well as for measurement and inspection of industrial components, for printed circuit and semiconductor die or wafer inspection and for similar noncontact measurement applications.

#### FAIRCHILD WESTON

#### **CCD IMAGING DIVISION**

#### CCD 111 256-Element Line Scan Image Sensor

#### **FEATURES**

- 256 × 1 photosité array

- 13µm × 17µm photosites on 13µm pitch

- Dynamic range typical: 7000:1

- On-chip video and compensation amplifiers

- Low power requirements

- All operating voltages 15V and under

- Low noise equivalent exposure

- Dimensionally precise photosite spacing

#### DESCRIPTION

The CCD111 is a monolithic 258-element line image sensor. The device is designed for optical character recognition and other imaging applications that require high sensitivity and high speed. The CCD111 is pin-for-pin compatible with and a functional replacement for the CCD110F.

The cell size is 13  $\mu$ m (0.51 mils) by 17  $\mu$ m (0.67 mils) on 13  $\mu$ m (0.51 mils) centers. The device is manufactured using Fairchild Weston advanced charge-coupled device n-channel Isopianar buried-channel technology.

| PIN NAME             | DESCRIPTION                          |

|----------------------|--------------------------------------|

| PG                   | Photogate                            |

| ФХА, ФХВ             | Transfer Clocks                      |

| φ1A, φ2A<br>φ1B, φ2B | Transport Clocks                     |

| og                   | Output Gate                          |

| os                   | Output Source                        |

| OD                   | Output Drain                         |

| CS                   | Compensation                         |

| ФЯ<br>RD             | Source<br>Reset Clock<br>Reset Drain |

| TP                   | Test Point                           |

| Vss                  | Substrate (ground)                   |

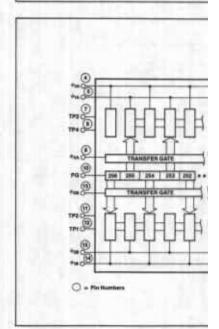

PIN CONNECTION DIAGRAM (TOP VIEW)

Fairchild Weston Systems, Inc. CCD Imaging Division 810 W. Maude Ave., Sunnyvale, California 94086 (408) 720-7600, TWX 910-373-2110

e 1988 Fairchild Weston Printed in U.S.A.

Fairchild Weston reserves the right to make changes in the circuitry or specifications at any time without notice

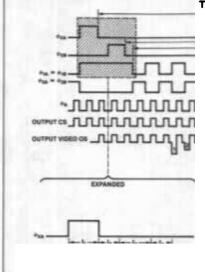

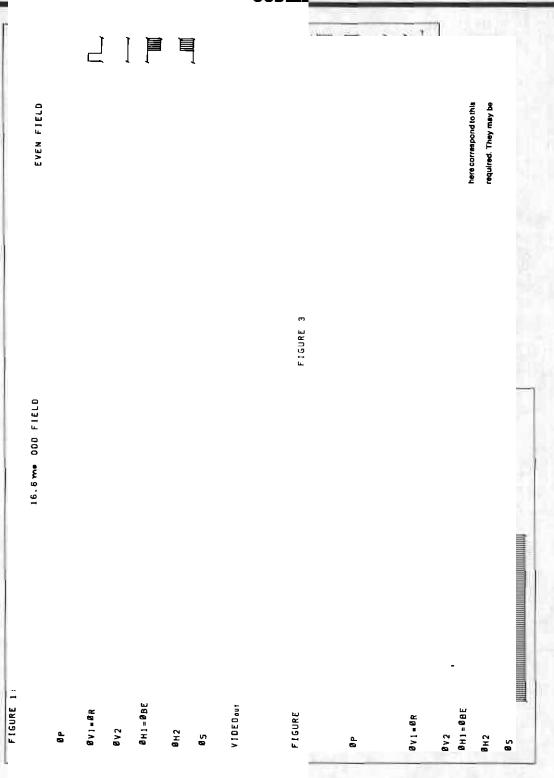

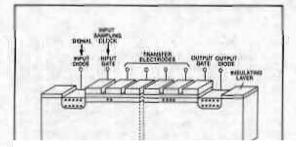

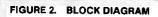

#### BLOCK DIAGRAM

(§) 42A

.

PG

Ŷχ

<u>}</u>@

#### **FUNCTIONAL DESCRIPTION**

The CCD111 consists of the following functional elements illustrated in the Block Diagram:

Image Sensor Elements — A row of 256 Image sensor elements separated by a diffused channel stop and covered by a silicon photogate. Image photons pass through the transparently of the single crystal silicon photogate and are absorbed in the single crystal silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

Two Transfer Gates — Gate structures adjacent to the row of image sensor elements. The charge packets accumulated in the image sensor elements are transferred out via the transfer gates to the transport registers whenever the transferred to voltages go HIGH. Alternate charge packets are transferred to the left and right transport registers. The transfer gates also control the integration time for the sensing elements.

Two 130-bit Analog Transport Shift Registers — One on each side of the line of image sensor elements and separated from it by a transfer gate. The two registers, called the transport registers, are used to move the light generated charge packets delivered by the transfer gates serially to the charge detector/amplifier. The complementary phase relationship of the last elements of the two transport registers provides for alternate delivery of charge packets to establish the original serial sequence of the line of video in the output circuit.

A Gated Charge Detector/Amplifier — Charge packets are transported to a precharged diode whose potential charges linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of the output n-channel MOS transistor producing a signal at the output

OS. A reset translator is driven by the reset clock  $(\phi R)$  and recharges the charge detector diode capacitance before the arrival of each new signal charge packet from the transport registers.

#### **DEFINITION OF TERMS**

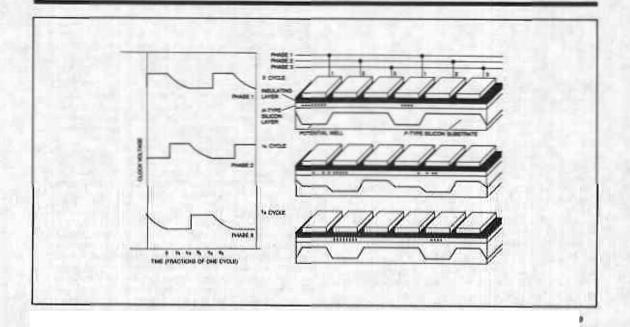

Charge-Coupled Device — A charge-coupled device is a semiconductor device in which finite isolated charge packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge packets are minority carriers with respect to the semiconductor substrate.

Transfer Clocks \$\phi\_A\$ \$\phi\_B\$.— The voltage waveforms applied to the transfer gates to move the accumulated charge from the image sensor elements to the CCD transport registers.

Transport Clocks \$\phi\_1\$, \$\phi\_2\$, \$\phi\_1\$, \$\phi\_2\$.— The two sets of 2-phase waveforms applied to the gates of the transport registers to move the charge packets received from the image sensor elements to the gated charge detector/amplifier.

Gated Charge Detector/Amplifier — The output circuit of the CCD111 that receives the charge packets from the transport registers and provides a signal voltage proportional to the size of each charge packet received. Before each new charge packet is sensed, a reset clock returns the charge detector voltage to a fixed level.

Reset Clock & — The voltage waveform required to reset the voltage on the charge detector.

Dynamic Range — The saturation exposure divided by the rms noise equivalent exposure. (This does not take into account dark signal components.) Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times rms noise.

RMS Noise Equivalent Exposure — The exposure level that gives an output signal equal to the rms noise level at the output in the dark.

Saturation Exposure — The minimum exposure level that will produce a saturation output signal. Exposure is equal to the irradiance times the photosite integration time.

Charge Transfer Efficiency — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

Responsivity — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

Total Photoresponse Non-uniformity — The difference of the response levels of the most and least sensitive element under uniform illumination. Measurement of PRNU excludes first and last elements. (See accompanying photos for details of definition.)

**Dark Signal** — The output signal in the dark caused by thermally generated electrons that is a linear function of the integration time and highly sensitive to temperature. (See accompanying photos for details of definition.)

Saturation Output Voltage — The maximum useable signal output voltage. Charge transfer efficiency decreases sharply when the saturation output voltage is exceeded.

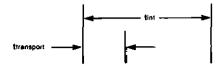

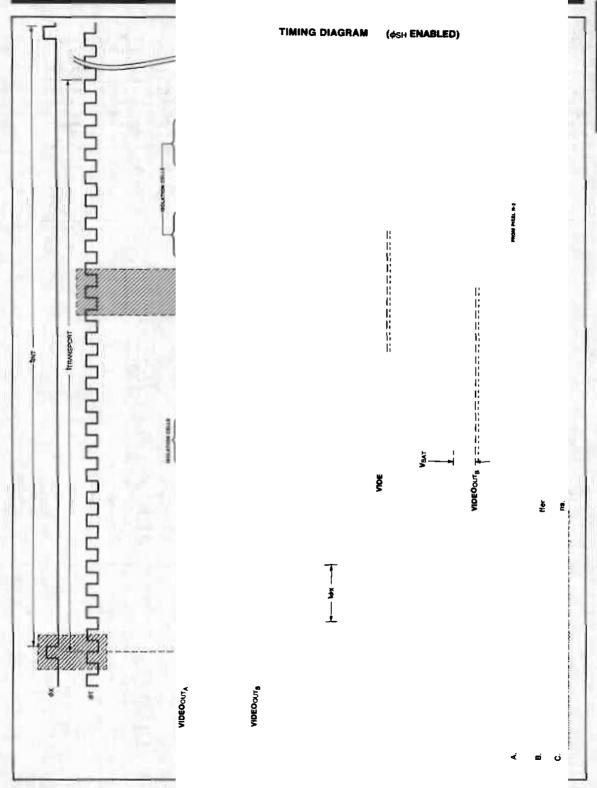

**Integration Time** — The time interval between the falling edges of any two transfer pulses  $\phi_{XA}$  or  $\phi_{XB}$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

Pixel - A picture element (photosite).

Peripheral Response — The output signal caused by lightgenerated charge that is collected by the transport registers (Instead of the the photosites). The primary cause of peripheral response on CCD111A/B devices manufactured after date code 81-01 is optical crosstalk from the photosites to the shift registers.

Major Differences Between the CCD111A and CCD111B

Both the CCD111A and the CCD111B have the same responsivity to visible light (400-700nm). The peripheral differences are as follows:

The CCD111A is intended for use in applications where very low dark signal and high responsivity to very near-infrared (700-900nm) light are needed, and where peripheral response is not critical.

The CCD111B is selected for use in applications where standard responsivity to very near-infrared (700-900nm) light and standard dark signal are acceptable and where peripheral response needs to be minimized.

It is not recommended that either part be used with illumination containing wavelengths greater than 900nm (near-infrared). If use of such a light source (unfiltered tungsten, for example) is unavoidable, the CCD111B will generally provide the user with more satisfactory results. The table on performance characteristics provides more information.

#### Absolute Maximum Ratings

Storage Temperature Operating Temperature Pins 2, 3, 4, 5, 6, 7, 10, 12, 13, 14, 15 Pins 1, 8, 11, 16 Pins 17, 18 Pin 19

-25°C to 55°C -0.3V to 15V -0.3V to 18V output, no voltage applied

-25°C to 100°C

**TEST LOAD CONFIGURATION**

DC CHARACTERISTICS: Tc = 25°C (Note 1)

SYMBOL CHARACTERISTIC LIMITS

TYP

15.0

CLOCK CHARACTERISTICS: T<sub>C</sub> = 25°C (Note 1)

AC CHARACTERISTICS: T<sub>c</sub> = 25°C, 1 $\phi_R$  = 1.0MHz, t<sub>int</sub> = 320  $\mu$ s, t<sub>transport</sub> = 259  $\mu$ s, Light Source = 2854°K + filters as specified. All operating voltagee nominal specified values. (Note 1) All tests done using "Test Load Configuration."

|        | voltages nominal specified value | BS. (Note 1) All | testa done usi       | ng "Test Lo | ad Configurati          | on."                  |

|--------|----------------------------------|------------------|----------------------|-------------|-------------------------|-----------------------|

| SYMBOL | PARAMETER                        |                  | RANGE                |             |                         | CONDITION             |

| SIMBOL |                                  | MIN              | TYP                  | MAX         | UNIT                    | CONDITION             |

| DR     | Dynamic Range                    |                  |                      |             |                         |                       |

|        | (relative to rms noise)          |                  | 7000:1               |             |                         | Note 7                |

|        | (relative to peak-to-peak noise) |                  | 1400:1               |             |                         |                       |

| NEE    | RMS Noise                        |                  |                      |             |                         |                       |

|        | Equivalent Exposure              |                  | 2 × 10 <sup>-2</sup> |             | $\mu$ J/cm <sup>2</sup> |                       |

| SE     | Saturation Exposure              |                  | 0.5                  |             | /cm²لير                 |                       |

| CTE    | Charge Transfer Efficiency       | .99990           | .99999               |             |                         | Note 8                |

| P      | Power Dissipation                |                  | 100                  |             | mW                      | V <sub>OO</sub> = 15V |

| z      | Output Impedance                 |                  | 1000                 |             | Ω                       |                       |

| N      | RMS Noise                        |                  | 100                  |             | μ۷                      |                       |

| 1      | Peak-to-Peak Noise               |                  | 500                  |             | μV                      |                       |

PERFORMANCE CHARACTERISTICS: T<sub>p</sub> = 25°C, fφ<sub>R</sub> = 1.0MHz, t<sub>int</sub> = 320 μs, t<sub>transport</sub> = 259 μs, Light Source = 2854°K + filters as specified. All operating voltages nominal specified values (Note 1)

> <1 <1 25

#### NOTES:

- To is defined as the package temperature, measured on the back surface of the ceramic header.

- 2. Negative transients on any clock pin going below 0.0V may cause charge injection that results in an increase in the apparent Dark Signal.

- 3. Vonu should track VRD.

L. (d) R. (d) A. (d) R.

k-to-Peak (temporal) Noise."

∋ for every 5°C incerase in T<sub>C</sub>. The shift register component is also inversely

11 Single-pixel Dark Signal non-uniformity (SPDSNU) approximately doubles for every 8°C increase in T<sub>C</sub>. They are also directly proportional to the integration time time.

+ SPOSNU.

ladiant Energy measured over the 350 nm - 1200 nm band." The device will not e radiant energy from a 2854° K source is at  $\lambda > 1200$  nm. For the unfiltered 2854° K -0.3X of the responsivity values for light measured over 350 nm <  $\lambda$  < 1200 nm Band Hot Mirror" (Optical Coating Labs, Inc., Santa Rosa, California) and one 2.0 a) filter in series. The "900 nm cutoff" filter is available on special order, consult I for the two cutoff filters and Spectral Energy Distribution curves for these filters section of this data sheet. It should be noted that the "2854" K + 700 nm cutoff"

ill PRNU measurements exclude the outputs from the first and last photoelements earray divided by the diameter of the lens aperature. As I number increases, the lons to dominate and increase the PRNU. A lower f number (f≤5) results in leas

17. See test load configuration.

#### **PHOTOELEMENT DIMENSIONS**

#### **PHOTOGATE**

SERPENTINE CHANNEL STOP

> ALUMINUM LIGHT SHIELD

ALL DIMENSIONS ARE TYPICAL VALUES.

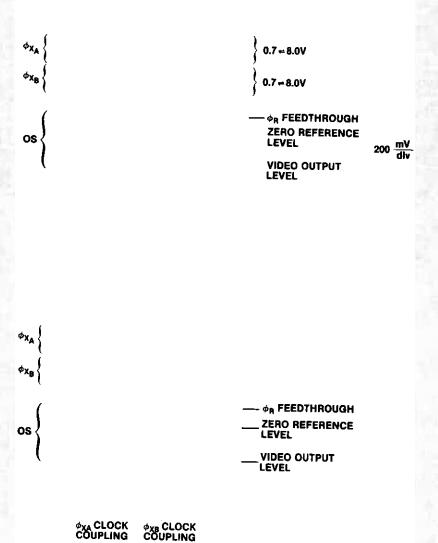

#### **OUTPUT WITH UNIFORM ILLUMINATION**

----- ØR CLOCK FEEDTHROUGH

ZERO REFERENÇE LEVEL

**TEST CONDITIONS:**  $T_C + 25^{\circ}C$ ,  $t_{int} = 640 \,\mu$ s,  $f_{\phi} = 512 \,\text{kHz}$ , "typ" voltage inputs,  $2854^{\circ}\text{K} + 700 \,\text{nm}$  cutoff filter set. (Half standard test speeds for clearer photos.)

= 10 VDC

100m\

#### **OUTPUT OF TWO PIXELS**

#### DEVICE ILLUMINATED

φ<sub>R</sub> RESET CLOCK FEEDTHROUGH

\_\_\_\_ZERO REFERENCE LEVEL ≈ 10 VDC

VIDEO OUTPUT (V<sub>OUT</sub>)

FROM PIXEL I FROM PIXEL (i + 1)

**DEVICE IN DARK**

BACKGROUND DARK SIGNAL

\_ZERO REFERENCE LEVEL ~ 10 VDC

TEST CONDITIONS: T<sub>C</sub> + 25°C, t<sub>int</sub> = 640  $\mu$ s, t<sub> $\phi$ </sub> = 512 kHz, "typ" voltage inputs, 2854°K + 700 nm cutoff filter set. (Half standard test speeds for clearer photos.)

#### PHOTORESPONSE NON-UNIFORMITY

MEASURED AT  $V_{OUT} = 350$  mV; ALL PRNU COMPONENTS EXCLUDE PIXELS #1 AND #256.

PRNU OF ALL PIXELS

**PIXEL #256**

LOW-FREQUENCY PRNU

PEAK-TO-PEAK PRNU

"DROP" DUE TO HIGH RESPONSIVITY OF PIXELS NEAR AMPLIFIER

> VIDEO OUTPUT LEVEL ADJACENT TO PRNU SINGLE-PIXEL NON-UNIFORMITY

TEST CONDITIONS: T<sub>C</sub> =  $+25^{\circ}$ C, t<sub>int</sub> = 320  $\mu$ s, f<sub> $\phi$ R</sub> = 1.0 MHz, 2854°K + 700 nm cutoff filter set, "typ" voltage inputs.

#### DC + LOW FREQUENCY DARK SIGNAL

AT  $t_{int} = 640 \mu s$ :

t<sub>integration</sub>

ZERO REFERENCE ≈ 10 VDC

SHIFT-REGISTER COMPONENT

REGISTER IMBALANCE

DC-COMPONENT

LOW-FREQUENCY COMPONENT

AT  $t_{int} = 900\mu s$ , OTHER INPUTS SAME AS ABOVE:

DC-COMPONENT

LOW-FREQUENCY COMPONENT

TEST CONDITIONS:  $T_C=+25^{\circ}C$ ,  $t_{\rm int}=$  (as above),  $t_{\phi R}=512$  kHz, "typ" voltage inputs, (Half standard test speeds for clearer photos.)

#### SINGLE-PIXEL DARK SIGNAL NON-UNIFORMITY

DC + LOW FREQUENCY

ZERO REFERENCE LEVEL ≈ 10 VDC

**TEST CONDITIONS:**  $T_C = +25^{\circ}$ C,  $t_{int} = 2.560$ ms,  $t_{\phi R} = 128$  kHz, "typ" voltage Inputs. (One-eight standard test speeds to emphasize Dark Signal.)

#### PERIPHERAL RESPONSE

ZERO REFERENCE LEVEL

≈ 10 VDC

PERIPHERAL RESPONSE

---VIDEO OUTPUT LEVEL

**TEST CONDITIONS:**  $T_C = +25^{\circ} C$ ,  $t_{int} = 640 \ \mu s$ ,  $t_{\phi R} = 510 \ kHz$ , "typ" voltage inputs, 2854° K + 700 nm cutoff filter set. (Haif standard test speeds for clearer photos.)

φX (TRANSFER CLOCK) COUPLING INTO OS (OUTPUT)

**DEVICE CARE AND OPERATION**

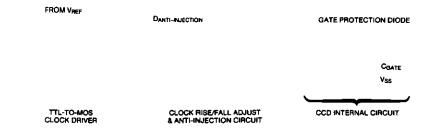

Charge Injection: Every input pin has a gate protection structure that includes a diode from the input to the (grounded) substrate Vss. The diode is reverse-biased during normal operation (V<sub>IN</sub> > Vss). Negative (transient) input voltages (V<sub>IN</sub> < Vss) will forward-bias the diode, injecting electrons into the bulk silicon of the CCD chip.

If sufficient charge is injected, it will accumulate in the transport register(s) and/or the photosites near the injecting gate protection structure(s). Injected charge which accumulates in the photosites will typically result in an apparent bell-shaped increases in Dark Signal (≈ 20-200 pixels wide) near the injecting gate protection structure. Injected charge which accumulates in a transport register will result in an apparent uniform Increase in that register's low frequency dark signal, creating a noticeable increase in the apparent Register Imbalance ("odd/even") of the Dark Signal.

The susceptibility to charge injection sufficient to increase the DC and Low Frequency Dark Signal varies significantly from device to device. It is not possible to select devices with "low" susceptibility. However, devices with low Dark Signal are typically more susceptible than devices with high Dark Signal.

Sufficient charge to appear as increased DC and Low Frequency Dark Signal may be injected by negative transient voltages < 4 ns long. Since these transients cannot be detected by oscilloscopes with less than 250-500 MHz bandwidth, a system which appears to be free from negative transients on a 200 MHz scope may still be prone to charge injection. The recommended method to eliminate charge injection is the following diode clipper circuit with suitable damping resistors between the clock drivers and the CCD111:

+5 TO +

Since  $C_{\phi R} << C_{\phi 1} \sim C_{\phi 2} \sim (3 \cdot C_{\phi X})$ , the damping resistors should be selected so that  $R_{\phi R} >> R_{\phi 1} = R_{\phi 2} \sim (1/3 \cdot R_{\phi X}.)$

It is also important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The DC and Low Frequency Dark Signal approximately doubles for every 5°C temperature increase and Dark Signal Non-Uniformities approximately double for every 8°C increase. The devices may be cooled to achieve very long integration times and very low light level capability.

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with delonized water. Allow the glass to dry, preferably by blowing with filtered dry  $N_2$  or air.

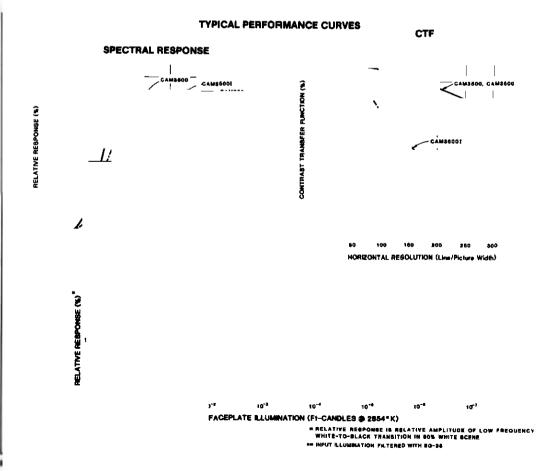

#### TYPICAL PERFORMANCE CURVES

TYPICAL SPECTRAL RESPONSE

OUTPUT NIGHAL LEVEL VERBUS

BYTEGRATION THE 2004 K TUNOSITEN

SOURCE WITH BIG-38 AND WHIM PLTEN

Told the control of the control of

#### TYPICAL PERFORMANCE CURVES (cont'd)

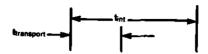

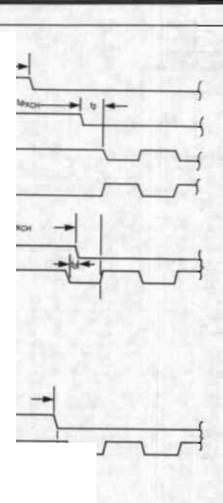

g requirements for transfer Gain Pulsas  $\phi_{XA}, \phi_{XB}$  quirement for  $t_2$  -  $\phi_{XA}$  may be tied to  $\phi_{XB}$

20ne < (1, = t<sub>s</sub>) < 60ne

1, =  $t_i < z_{i,m}$ 0.2( $t_{i,m}$ ) <  $t_{i,m}$  < 0.3( $t_{i,m}$ ) Timing requirements for  $\phi_{i,k} \phi_{i,0}$

20mt < (1, = 1,) < 100ms

$\phi_1$  and  $\phi_2$  clocks may not both be < 3.6V simultaneously.

# VIDEO DATA VALID FROM REGISTER A

#### **ORDER INFORMATION**

It is Important to note that two different selections of the CCD111 are being offered for applications that differ in the wavelength of light used for imaging. Please refer to the section "Major Differences Between the CCD111A and CCD111B" on page 13 before placing an order.

To order the CCD111, please follow the ordering codes listed in the table below:

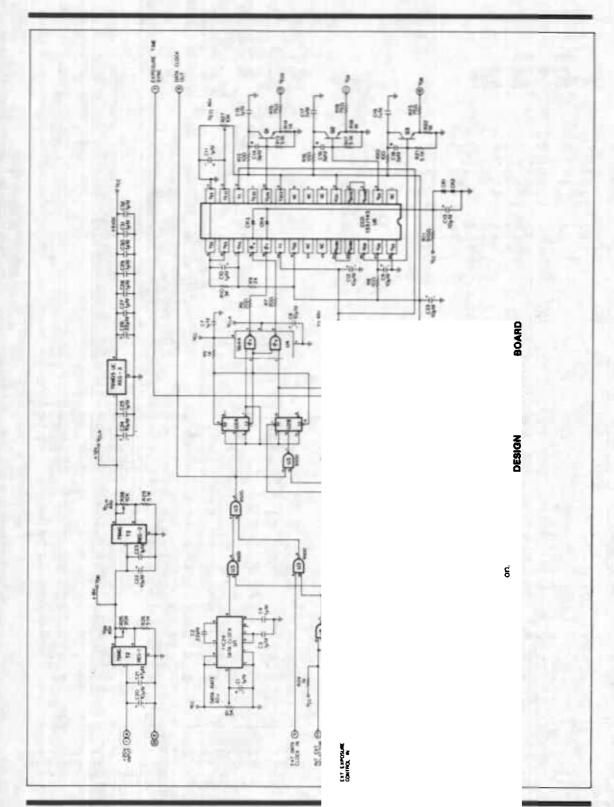

A printed circuit board is available which includes all the necessary clocks, logic drivers, and video amplifiers to operate the CCD111. The board is fully assembled and tested and requires ±15V and +5V supplies for operation. The printed circuit board order code is I-SCAN.

CCD111A 256 × 1 Line Image Sensor CCD111B 256 × 1 Line Image Sensor

CCD111DC Package Outline 18-Pin Dual In-Line Ceramic Package

> 0.048 (1.22) TOP OF DIE TO TOP OF COVER

#### FAIRCHILD WESTON

#### CCD IMAGING DIVISION

#### CCD122 1728-Element Linear Image Sensor

#### **FEATURES**

- 1728 × 1 photosite array

- 13μm × 13μm photosites on 13μm pitch

- Low dark signal

- High responsivity

- On-chip clock drivers

- Dynamic range typical: 5500:1

- Over 1V peak-to-peak output

- Dark and white references contained in a sampled-and-held output

- Special selections available consuit factory.

#### DESCRIPTION

The CCD122 is a monotlithic 1728-element linear image sensor, designed for page scanning applications including facsimile, optical character recognition and other imaging applications which require high resolution and high sensitivity.

The 1728 sensing elements of the CCD122 provide a 200-line per inch resolution across an 8-1/2 inch page adopted as an international facsimile standard.

The CCD122 also incorporates on-chip clock driver circuitry.

The photoelement size is 13  $\mu$ m (0.51 mils) by 13  $\mu$ m (0.51 mils) on 13  $\mu$ m (0.51 mils) centers. The devices are manufactured using Fairchild Weston advanced charge-coupled device n-channel Isoplanar buried-channel technology.

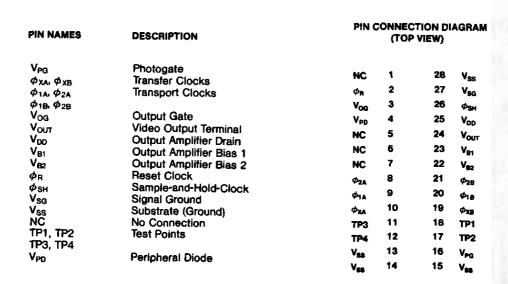

| PIN NAME        | E DESCRIPTION  Photogate | PIN CONNECTION DIAGRAM<br>(TOP VIEW) |    |                   |  |

|-----------------|--------------------------|--------------------------------------|----|-------------------|--|

| V <sub>PG</sub> |                          | 4. 1                                 | 24 | u                 |  |

|                 |                          |                                      | 23 |                   |  |

|                 |                          |                                      | 22 |                   |  |

|                 |                          |                                      | 21 | :O <sub>OUT</sub> |  |

|                 |                          |                                      | 20 |                   |  |

|                 |                          |                                      | 19 |                   |  |

|                 |                          |                                      | 18 | DUT               |  |

|                 |                          |                                      | 17 |                   |  |

Fairchild Weston Systems, Inc. CCD Imaging Division. 810 W. Maude Ave., Sunnyvale, California 94086 (408) 720-7800, TWX 910-373-2110

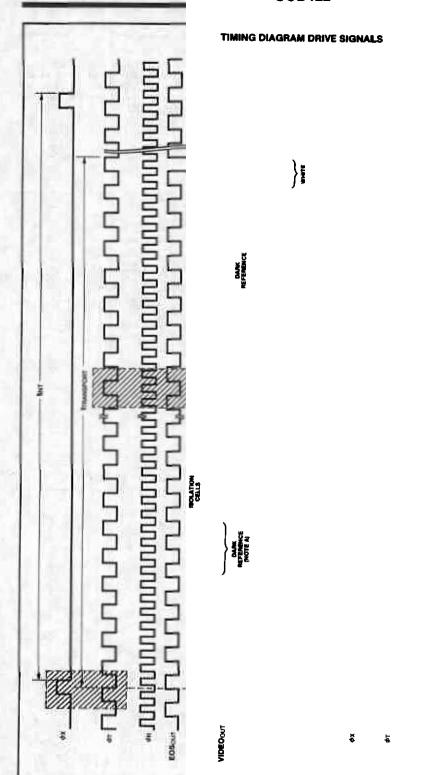

BLOCK DIAGRAM

\$@ @**@**@

22 22

**(1)**

VEI

0

₩ (3) VIDEOOUT

O = OCD122 Ple Humbs O = Dest Reference

if a White Relevator

CCD122: N = 1738

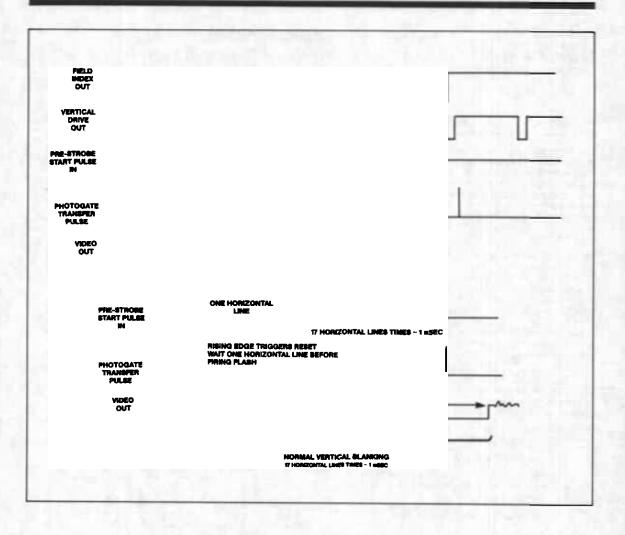

#### **FUNCTIONAL DESCRIPTION**

Image Sensor Elements — A line of 1728 image sensor elements separated by diffused channel stops and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon dioxide layer and are absorbed in the single crystal silicon creating held-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated noise background at zero illumination to a maximum at saturation under bright illumination.

Transfer Gate — Gate structure adjacent to the line of image sensor elements. The charge-packets accumulated in the image sensor elements are transferred out via the transfer gate to the transport registers whenever the transfer gate voltage goes HiGH. Alternate charge-packets are transferred to the analog transport shift registers. The transfer gate also controls the exposure time for the sensing elements and permits entry of charge to the End-Of-Scan (EOS) shift registers creating the end-of-scan waveform.

Four 879-Bit Analog Shift Registers — Two on each side of the line of image sensor elements and separated from it by the transfer gate. The two inside registers, called the transport shift registers, are used to move the image generated charge-packets delivered by the transfer gate serially to the charge-detector/amplifier. The complementary phase relationship of the last elements of the two transport shift registers provides for alternate delivery of charge-packets to establish the original serial sequence of the line of video in the output circuit. The outer two registers serve to deliver the end-of-scan waveform and reduce peripheral electron noise in the inner shift registers.

Gated Charge-Detector/Amplifier — Charge-packets are transported to a precharged diode whose potential charges linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of an n-channel MOS transisitor producing a signal which passes through the sample-and-hold gate to the output at VIDEOout. The sample-and-hold gate is a switching MOS transistor in the output amplifier that allows the output to be delivered as a sampled-and-held waveform. A reset transistor is driven by the Reset Clock ( $\phi_R$ ) and recharges the charge-detector diode capacitance before the arrival of each new signal charge-packet from the transport registers.

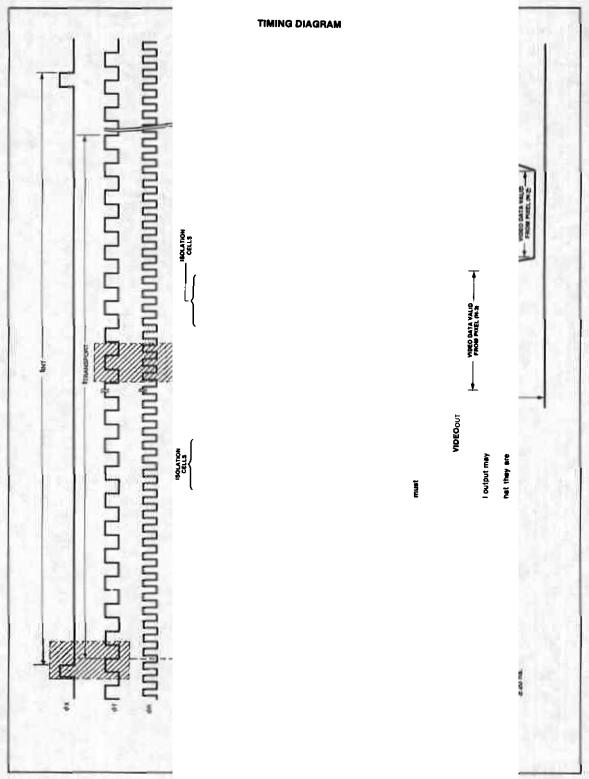

Clock Driver Circuitry — Allows the CCD122 to be operated using only three external clocks, (1) a Reset Clock signal which controls the integrated output signal amplifier, (2) a square wave Transport Clock which operates at half the reset clock frequency and controls the readout rate of video data from the sensor, and (3) a Transfer Clock pulse which controls exposure time of the sensor. The external clocks should be able to suppy TTL level power.

Dark and White Reference Circuitry — Four additional sensing elements at both ends of the 1728 array are covered by opaque metalization. They provide a dark (no illumination) signal reference which is delivered at both ends of the line of video output representing the illuminated 1728 sensor elements (labelled "D" in the block diagram). Also included at one end of the 1728 sense element array is a white signal reference level generator which likewise provides a reference in the output signal (labelled "W" in the block diagram). These reference levels are useful as inputs to external DC restoration and/or automatic gain control circuitry.

#### **DEFINITION OF TERMS:**

Charge-Coupled Device — A charge-coupled device is a semiconductor device in which finite isolated charge-packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge-packets are minority carriers with respect to the semiconductor substrate.

**Transfer Clock**  $\phi_X$  — The voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD transport shift registers.

**Transport Clock**  $\phi_T$  — The clock applied to the gates of the CCD transport shift registers to move the charge-packets received from the image sensor elements to the gated charge-detector/amplifier.

Reset Clock  $\phi_R$  — The voltage waveform required to reset the voltage on the charge-detector.

Sample-and-Hold Clock  $\phi_{SH}$  — An internally supplied voltage waveform applied to the sample-and-hold gate in the amplifier to create a continuous sampled video signal at the output. The sample-and-hold feature can be defeated by connecting  $\phi_{SH}$  to  $V_{DD}$ .

Dark Reference — Video output level generated from sensing elements covered with opaque metalization providing a reference voltage equivalent to device operation in the dark. Permits use of external dc restoration circuitry.

Isolation Cell — A site on-chip producing an element in the video output that serves as a buffer between valid video data and dark and white reference signals. The output from an isolation cell contains no valid video information and should be ignored.

Peak-to-Peak Noise Equivalent Exposure — The exposure level which gives an output signal equal to the peak-to-peak noise level at the output in the dark.

Saturation Exposure — The minimum exposure level that will produce a saturated output signal. Exposure is equal to the light intensity times the photosite integration time.

**Charge Transfer Efficiency** — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

**Reaponsivity** — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure level.

**Dark Signal** — The output signal in the dark caused by thermally generated electrons which is a linear function of integration time and highly sensitive to temperature. (See accompanying photos for details of definition.)

Total Photoresponse Non-Uniformity — The difference of the response levels between the most and least sensitive elements under uniform illumination. (See accompanying photos for details of definition.)

**Integration Time** — The time interval between the falling edges of any two successive transfer pulses  $\phi_X$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

Pixel - Picture element (photosite).

**TEST LOAD CONFIGURATION**

END-OF-SCAN WAVEFORM

PHOTOELEMENT DIMENSIONS

#### ABSOLUTE MAXIMUM RATINGS (Above which useful life may be impaired)

Storage Temperature Operating Temperature

CCD122 Pins 1, 4, 9, 10, 11, 13, 14, 16, 22, 23

Pins 5, 12, 17, 24

Pins 2, 3, 6, 7, 8, 15, 19, 20,

Pins 16, 21

CAUTION NOTE: These devices have limited built-in gete protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins VIDEO<sub>OUT</sub> and EOS<sub>OUT</sub> to V<sub>SS</sub> or V<sub>DO</sub> during operation of the device. Shorting these pins temporarily to V<sub>SS</sub> or V<sub>DO</sub> may destroy the output amplifiers.

| OC CHAR! |                                       |      |      |      |    |        |     |

|----------|---------------------------------------|------|------|------|----|--------|-----|

| SYMBO    |                                       |      |      |      |    | NDITIO | NS  |

|          |                                       | 12.0 |      |      |    |        | ı   |

|          | Clock Driver Drain Supply Current     |      | 6.9  | 12.5 | mA |        |     |

|          | Output Amplifier Drain Supply Voltage | 12.0 | 13.0 | 14.0 | ٧  |        | - 5 |

| loo      | utput Amplifier Drain Supply Current  |      | 6.9  | 12.5 | mA |        |     |

|          | Photogate Blas Voltage                | 6.5  | 7.0  | 7.5  | ٧  |        |     |

| VT       | DC Electrode Blas Boltage             | 4.5  | 5.0  | 5.5  | ٧  | Note 2 |     |

| VEI      | Electrical Input Blas Voltage         |      | 11.4 |      | ٧  | Note 3 |     |

| Vss      | Substrate (Ground)                    |      | 0.0  |      | ٧  |        |     |

#### CHARACTERISTICS: (Note 1)

= 25°C, ton = 0.5 MHz, tint = 10 ms, light source = 2854°K + 3.0 mm thick Corning 1-75 IR-absorbing filter. All nominal specified values. All tests done using "Test Load Configuration."

#### CHARACTERISTIC

Dynamic Range

(relative to peak-to-peak noise)

#### CLOCK CHARACTERISTICS: Tp = 25°C (Note 1)

#### PERFORMANCE CHARACTERISTICS: (Note 1)

$T_P = 25$  °C,  $t\phi R \approx 0.5$  MHz,  $t_{int} \approx 10$  ms, light source  $\approx 2854$  °K + 3.0 mm thick Corning 1-75 IR-absorbing filter All voltages nominal specified values.

#### CONDITIONS

| Photoresponse Non-uniformity                                      |    |         |

|-------------------------------------------------------------------|----|---------|

| Peak-to-Peak                                                      | m∨ | Note 16 |

| Peak-to-Peak without Single-Pixel Positive<br>and Negative Pulses | mV | Note 16 |

| Single-pixel Positive Pulses                                      | m۷ | Note 16 |

| Single-pixel Negative Pulses                                      | mV | Note 16 |

|                                                                   | mV | Note    |

Notes 13, 14

14

ting less

Notes 13, 15

Note 17

Note 18

PRNU Measurements taken at 700 mV output level using an t/2.8 lens and excluded the outputs from the first and lest elements of the array, number is defined as the distance from the lens to the array divided by the diameter of the lens aperture. As the f number increases, the resulter highly, collimated light causing device photoelle blemishes to dominate the PRNU.

#### NOTES:

- 1. TP is defined as the package temperature.

- 2. VT should be equal to (1/2) VeTH.

- VEI is used to generate the end-of-scan output and the white reference output. These two signals can be eliminated by connecting VEI to a voltage level equal to V\$XH + 5 V.

- 4. Negative transients on any clock pin going below 0.0 V may cause charge-injection which results in an increase of apparent DS

- 5. C4T ≈ 700 pF

- 6. C4X = 300 pF

- 7. CéR ≅ 5 pF

- 8. Minimum clock frequency is limited by increase in dark signal.

- 9. Dynamic range is defined as VSAT/peak-to-peak (temporal) or VSAT/rms polse.

- 10. 1 pl/cm2 = 0.02 fcs at 2854°K, 1 fcs = 50 pl/cm2 at 2854°K.

- 11. SE for 2864°K for light without 3.0 mm thick Corning 1-75 iR-absorbing filter is typically 0.8 al/cm².

- 12. CTE is the measurement for a one-stage transfer.

- 13. See photographs for DS definitions.

- 14. Dark signal component approximately doubles for every 5°C increase in TP.

- Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU. The SPDSNU approximately doubles for every 8°C increase in TP.

- 16. See photographe for PRNU definitions.

- 17. Responsivity for 2854\*K right source without 3.0 mm thick Corning 1-75 (Rebsorbing filter is typically 2 V per pl/cm2,

- 18. See test load configurations.

#### PHOTORESPONSE NON-UNIFORMITY PARAMETERS (PRNU)

Zero Reference Level (# + 5.5 Vdc)

Per Wit Por No

500 ps

TEST CONDITIONS

TP  $a + 25^{\circ}$ C,  $t_{e}$ R = 0.5 MHz,  $t_{tot}$  = 10.0 ms, all voltages norminal spec-sheet values. Humination: 2854°K source with a 3.0 mm thick Coming 1-75 iR-absorbing filter. PRNU measurements taken at an output voltage of 700 mV.

#### PRNU PARAMETERS (CONTINUED)

nv

mil

Clock Feedthrough

#### TEST CONDITIONS

TP at + 25°C, feR = 0.5 MHz, tint = 10.0 me, all voltages nominal spec-sheet values. Humination: 2854°K source with a 3.0 mm thick Coming 1-75 IR-absorbing filter. PRNU measurements taken at an output voltage of 700 mV.

#### DARK SIGNAL PARAMETERS (DS)

Zero Reference Level (a + 5.5 Vdc)

Total Dark Signal

10 mV

Zero Reference Level (≥ +5.5 Vdc)

10 mV

TEST CONDITIONS

TP  $\approx$  +25°C, feR = 0.5 MHz, tnt = 10.0 ms, all voltages nominal specified values

#### DS PARAMETERS (CONTINUED)

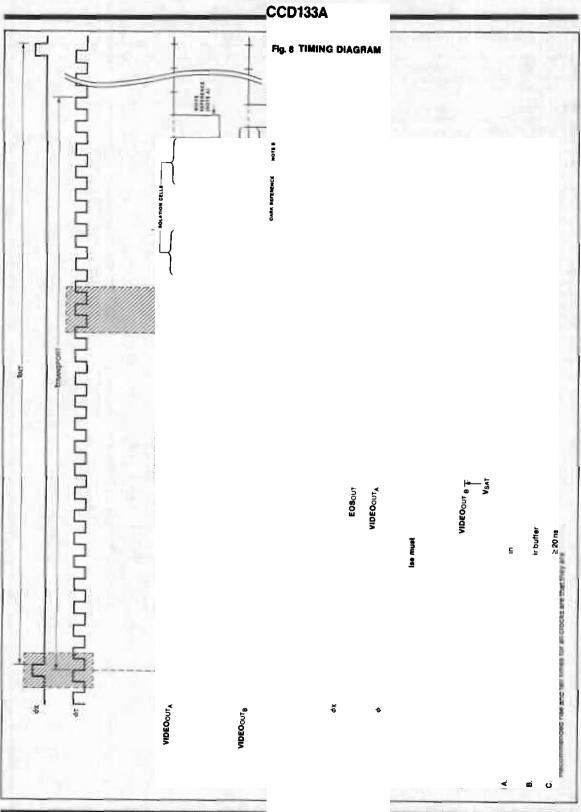

#### VIDEO OUTPUT TIMING PHOTOGRAPHS

TEST CONDITIONS

TP s + 25°C, far = 0.6 MHz, tint = 10 ms, all voltages nominal specialiset values. Illumination: 2654°K source with a 3.0 mm thick Coming 1-75 IR-absorbing filter. PRNU measurements taken at an output voltage of 700 mV.

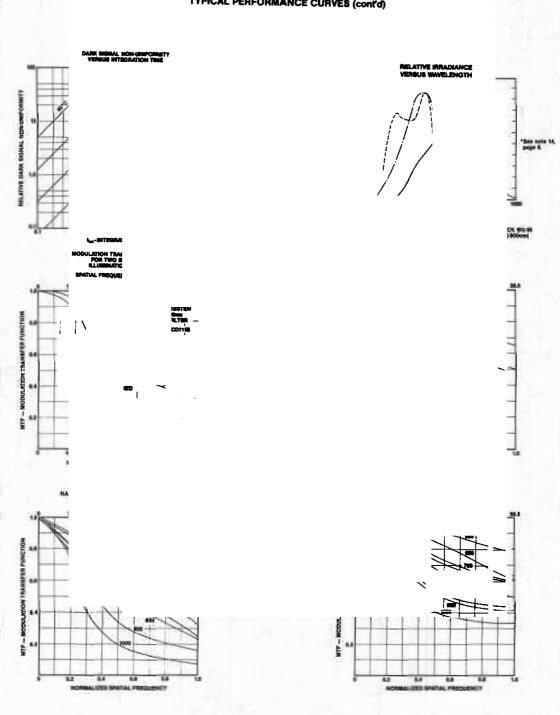

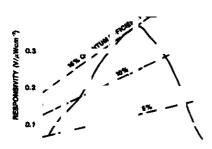

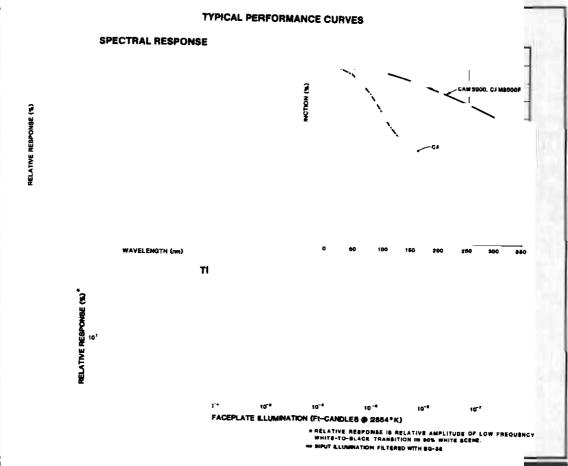

# TYPICAL PERFORMANCE CURVES

TYPICAL SPECTRAL RESPONSE

DC AND LOW-FREQUENCY DARK SIGNAL VERSUS INTEGRATION TIME

RESPONSIVITY VIJJem-2

$\label{eq:total_state} \begin{array}{ll} & \text{10} & \text{10} \\ \\ t_{\text{ini}} = & \text{INTEGRATION TIME} = \text{me} \end{array}$

MODULATION TRANSFER FUNCTIONS FOR NARROW BAND ILLUMINATION SOURCES SPATIAL FREQUENCY—CYCLES/mm

OUTPUT SIGNAL LEVEL VERSUS INTEGRATION TIME 2854°K TUNGSTEN SOURCE WITH CORNING 1-75 FILTER

8

0.4 0.6 0.0

6 20 4.0 6.0 6.0 10.0 10.0 1<sub>int</sub> — INTEGRATION TIME — ms

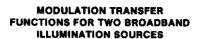

MODULATION TRANSFER FUNCTIONS FOR TWO BROADBAND ILLUMINATION SOURCES

SPATIAL FREQUENCY - CYLES/mm

¥è

$t_{\rm int} \sim INTEGRATION TIME - me$

NORMALIZED SPATIAL FREQUENCY

The Coming 1-75 filter has the following typical transmittance spectral characteristic: >85% at <800 nm, 60% at 700 nm, 30% at 800 nm, 5% at 900 nm and <2% at >1000 nm.

part of their buf-

re that they are

>20 nn.

## **DEVICE CARE AND OPERATION:**

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with de-ionized water. Allow the glass to dry preferably by blowing with filtered dry  $N_2$  or air.

It is important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The dark signal DC and low frequency components approximately double for every 5°C temperature increase and single-pixel dark signal non-uniformities approximately double for every 8°C temperature increase. The devices may be cooled to achieve very long integration times and very low light level capability.

**ORDER INFORMATION** — Order CCD122DC where "D" stands for a ceramic package and "C" for commercial temperature range.

Also available are CCD122DB Design Aid printed circuit boards that include all the necessary clocks, logic drivers and video amplifiers to operate the CCD122DC. The boards are fully assembled and tested and require only one power supply for operation (+15 V). See Page 135.

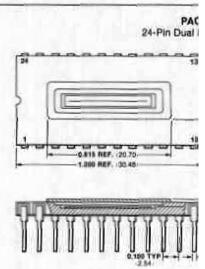

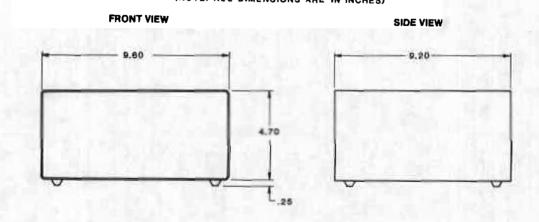

CCD122DC PACKAGE OUTLINE 24-Pin Dual In-line Ceramic Package

REF (27 43)

0.330 AEI

•

#### NOTES

All dimensions in inches (bold) and millimeters (parentheses). Header is black ceramic ( $Alg0_3$ ). Window is glass. The amplifier of the device is located near the notched end of the package.

# **CCD123** 1728-Element Linear Image Sensor

## **FEATURES**

D

- 1728 × 1 photoeite array

- $13\mu m \times 10\mu m$  on  $10\mu m$  pitch.

- Low dark signal.

- High responsivity.

- On-chip clock drivers.

- Dynamic range typical: 5500:1.

- Over 1V peak-to-peak output.

- Dark reference contained in a sampled-and-hold output

- Special selections available consult factory.

The photo-element size is  $10\mu m$  (0.39mils) by  $13\mu m$  (0.5mils) on  $10\mu m$  (0.39mils) centers. The devices are manufactured using Fairchild Weston advanced charge-coupled device nchannel isoplanar buried-channel technology.

22

21

20

19

18

17

16 15

Fairchild Weston Systems, Inc. CCD Imaging Division 810 W. Maude Ave., Sunnyvale, California 94088 (408) 720-7600, TWX 910-373-2110

●1986 Fairchild Weston Printed in U.S.A. Fairchild Weston reserves the right to make changes in the circuitry or specifications at any time without notice

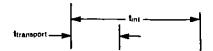

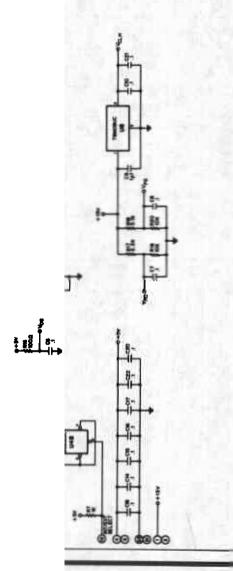

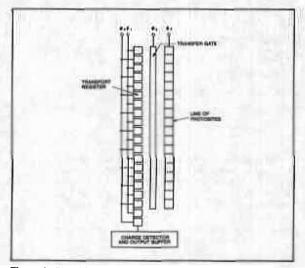

### Fig. 1 BLOCK DIAGRAM

CC0123 N = 1778 D = Dark Reference

#### FUNCTIONAL DESCRIPTION

The CCD123 consists of the following functional elements illustrated in the Block Diagram and circuit diagram (Fig. 1).

Photosites — A row of 1728 image sensor elements separated by a diffused channel stop and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

Photgate — The photogate structure, located at the edge of the photosites, provides a bias voltage for the photosites.

Transfer Gate — Gate structure adjacent to the line of image sensor elements. The charge-packets accumulated in the image sensor elements are transferred out via the transfer gate to the transport registers whenever the transfer gate voltage goes HIGH. Alternate charge-packets are transferred to the analog transport shift registers. The transfer gate also controls the exposure time for the sensing elements.

Four 879 Bit Analog Shift Registers — Two on each side of the line of image sensor elements and separated from it by the transfer gate. The two inside registers, called the transport shift registers, are used to move the image generated charge-packets delivered by the transfer gate serially to the charge-detector/amplifier. The complementary phase relationship of the last elements of two transport shift registers provides for alternate delivery of charge-packets to the establish the original serial sequence of the line of video in the output circuit. The outer two registers serve to reduce peripheral electron noise in the inner shift registers.

Gate Charge-Detector/Amplifier — Charge-packets are transported to a precharged diode whose potential charges linearly in response to the quantity of the signal charge delivered. This potential is applied to the gate of an n-channel MOS transistor producing a signal which passes through the sample-and-hold gate to the output at VIDEO<sub>OUT</sub>. The sample-and-hold gate is a switching MOS transistor in the output amplifier that allows the output to be delivered as a sample-and-held waveform. A reset transistor is driven by the Reset Clock ( $\phi$ R) and recharges the charge-detector diode capacitance before the arrival of each new signal charge-packet from the transport registers.

Clock Driver Circuitry — Allows the CCD123 to be operated using only three external clocks, (1) a Reset clock signal which controls the integrated output signal amplifier, (2) a square wave Transport Clock which operates at half the reset clock frequency and controls the readout rate of video data from the sensor, and (3) a Transfer Clock pulse which controls exposure time of the sensor. The external clocks should be able to supply TTL level power.

Dark Reference Output — Four additional sensing elements at both ends of the 1728 array are covered by opaque metalization. They provide a dark (no illumination) signal reference which is delivered at both ends of the line of video output representing the illuminated 1728 sensor elements (labelled "D" in the block diagram). The dark reference level is useful as an input to external DC restoration circuitry

#### **DEFINITION OF TERMS:**

**Transfer Clock**  $\phi X$  — The voltage waveform applied to the transfer gate to move the accumulated charge from the image sensor elements to the CCD transport shift registers.

**Transport Clock**  $\phi$ **T** — The clock applied to the gates of the CCD transport shift registers to move the charge-packets received from the image sensor elements to the gated charge-detector/amplifier.

**Reset Clock \phi R** — The voltage waveform required to reset the voltage on the charge-detector.

Sample-and-Hold Clock  $\phi$ SH — An internally supplied voltage waveform applied to the sample-and-hold gate in the amplifier to create a continuous sampled video signal at the output. The sample-and-hold feature can be defeated by connecting Pin V<sub>SD</sub> to V<sub>DD</sub>.

isolation Cell — A site on-chip producing an element in the video output that serves as a buffer between valid video data and dark reference signals. The output from an isolation cell contains no valid video information and should be ignored.

Dynamic Range — The saturation exposure divided by the RMS temporal noise equivalent exposure. Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times RMS noise.

RMS Noise Equivalent Exposure — The exposure level that gives an output signal equal to the RMS noise level at the output in the dark.

Seturation Exposure — The minimum exposure level that will provide a saturation output signal. Exposure is equal to the light intensity times the photosite integration time.

Charge Transfer Efficiency — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

Responsivity — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

**Dark Signal** — The output signal in the dark caused by thermally generated electrons which is a linear function of integration time and highly sensitive to temperature.

**Integration Time** — The time interval between the falling edges of any two successive transfer pulses  $\phi X$  as shown in the timing diagram. The integration time is the time allowed for the photosites to collect charge.

Total Photoresponse Non-Uniformity — The difference of the response levels of the most and the least sensitive element under uniform illumination. Measurement of PRNU excludes first and last elements.

Seturation Output Voltage — The maximum usable signal output voltage. Charge transfer efficiency decreases sharply when the saturation output voltage is exceeded.

Sample-and-Hold Load Points — Used to reduce charge injection which might be caused by the internal sample and hold clock. Connect 10pf to SH<sub>L</sub>1 and 56pf to SH<sub>L</sub>2.

Pixel — A picture element (photosite).

## Fig. 2 TEST LOAD CONFIGURATION

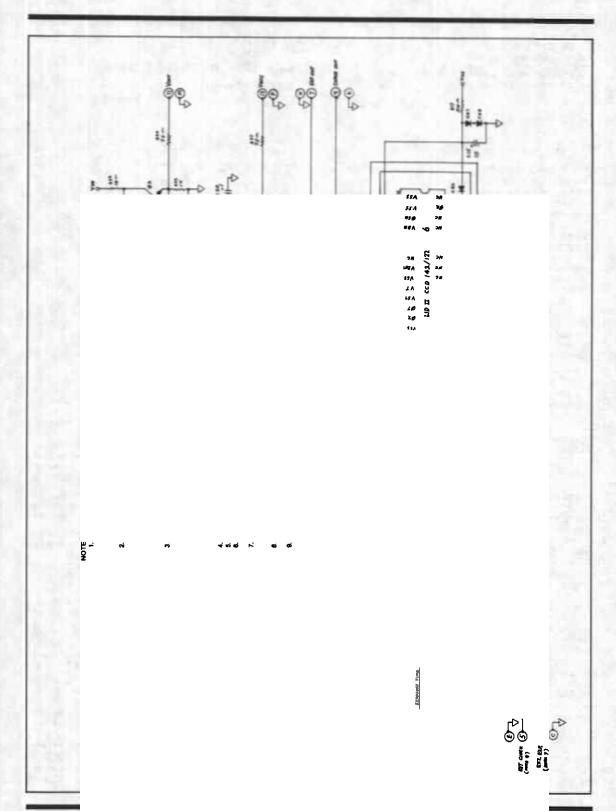

#### Fig. 3 PHOTOELEMENT DIMENSIONS

**ALL DIMENSIONS ARE TYPICAL VALUES**

|   | ABSOLUTE MAXIMUM RATINGS (Above which useful life may be impaired)                                                                                                                                                                                                                                  |                                                                                     |   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---|

|   | Storage Temperature                                                                                                                                                                                                                                                                                 | -25°C to +125°C                                                                     |   |

|   | Operating Temperature (See "Device Care & Operation")                                                                                                                                                                                                                                               | -25°C to +70°C                                                                      |   |

|   | CCD123 Pins 1, 4, 10, 11, 13, 14, 16, 22, 23                                                                                                                                                                                                                                                        | -0.3V to 18V                                                                        |   |

|   | Pins 5, 12, 17, 24                                                                                                                                                                                                                                                                                  | 0V                                                                                  |   |

|   | Pins 6, 7, 8, 15, 18, 19, 20,                                                                                                                                                                                                                                                                       | , NC                                                                                |   |

|   | Pins 2, 3, 21                                                                                                                                                                                                                                                                                       | See caution note                                                                    |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   | CAUTION NOTE: These devices have limited built-in gate protection. It is recommended that static discharge be control avoid shorting Vour. SH <sub>L</sub> and SH <sub>L</sub> 2 to Vss. Vsg. Vcg or Vpp during operation of these devices. Temporarily shorting there and/or the output amplifier. | olled and minimized. Care must be taken<br>g this pin may destroy the on-chip clock |   |

|   |                                                                                                                                                                                                                                                                                                     | -                                                                                   | _ |

| - |                                                                                                                                                                                                                                                                                                     | -                                                                                   | _ |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   | 8.0                                                                                                                                                                                                                                                                                                 |                                                                                     |   |

|   | Vss                                                                                                                                                                                                                                                                                                 |                                                                                     |   |

|   | Vsg                                                                                                                                                                                                                                                                                                 |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   | Vcg                                                                                                                                                                                                                                                                                                 |                                                                                     |   |

|   | Vso                                                                                                                                                                                                                                                                                                 |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     | -                                                                                   | - |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |

|   |                                                                                                                                                                                                                                                                                                     |                                                                                     |   |